I²C interface tutorial

- Geschiedenis van de I²C interface

- Fysieke eigenschappen van de I²C interface

- Start en stop condities op de I²C interface

- Dataoverdracht met I²C

- Synchronisatie en arbitrage

Geschiedenis van de I²C interface

In de late zeventiger jaren van de vorige eeuw begonnen kleine microprocessors en digitaal werkende geïntegreerde circuits langzaam taken over te nemen van analoge circuits in consumenten producten zoals televisies. Philips—één van de grote fabrikanten van consumentenelektronica—zocht naar een interface die zou kunnen worden gebruikt om ICs met elkaar te laten communiceren via een goedkope low-cost verbinding op niet al te extreme snelheden. De gebruikelijke methode van inter-IC communicatie op dat moment was via een parallelle 8 bit brede bus. Deze busstructuur—die ook gebruikt wordt om geheugen en randapparatuur te verbinden met een CPU—benodigt niet alleen acht datalijnen om de gegevens over te dragen, maar ook verscheidene lijnen voor het addresseren van specifieke randapparatuur ICs. Philips onderzocht de mogelijkheid om de hoeveelheid benodigde printplaat oppervlakte te beperken voor deze bussen evenals de ermee gemoeid gaande kosten door het aantal communicatielijnen te reduceren tot twee. Deze inter-IC bus werd IIC of I²C genoemd en werd wijd geïmplementeerd in situaties waarbij kosten en afmetingen reductie belangrijker waren dan datasnelheid.

Het lukte Philips om het aantal datalijnen van de I²C bus te reduceren door om te schakelen van parallelle naar synchroon seriële communicatie. De I²C bus heeft slechts twee lijnen waarbij één SDA genoemd wordt en de databits overdraagt en de tweede de naam SCL gekregen heeft en dient als kloksignaal. De berichten die worden verzonden over de I²C bus bevatten adressen die bepalen welk apparaat er op moet reageren. De I²C bus is zodanig ontworpen, dat het toegestaan is veel geïntegreerde circuits van verschillend model en ontwerp met elkaar te verbinden. Kleine filters aan de ingangszijde van de ontvanger van de ICs zijn geïmplementeerd om storingen te reduceren, en er zijn mogelijkheden dat tragere ICs de communicatie voor een korte tijd kunnen vertragen. Hoewel de eerste toepassing van de I²C in televisies was om audio- en videosignalen te regelen wordt de bus nu breed toegepast in allerlei besturings- en signaalverwerkingsapplicaties, bijvoorbeeld in de VGA interface of HDMI interface om video mode instellingen tussen de video controller en de aangesloten monitor uit te wisselen. Dit brede succes is voornamelijk te danken aan de veelzijdigheid van de bus.

- Elke deelnemer op de I²C bus heeft zijn eigen unieke adres

- Communicatie vindt plaats in master-slave mode, waarbij het ontwerp meerdere masters op één bus toestaat

- Collision detection mechanismen zijn aanwezig om te voorkomen dat meer dan één apparaat op een gegeven moment de bus gebruikt

- Communicatie tussen master en slave is bi-directioneel

- Meerdere snelheden zijn mogelijk. Huidige implementaties staan snelheden van 100, 400 en 3400 kbps toe. Deze datasnelheden dragen achtereenvolgens de namen standard-mode, fast mode en high-speed mode.

Fysieke eigenschappen van de I²C interface

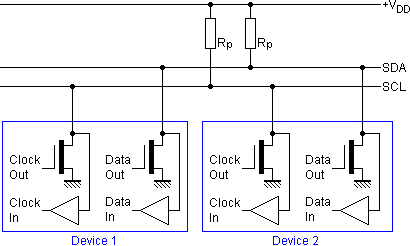

In het fysieke ontwerp van de I²C bus heeft Philips een datalijn SDA en een kloklijn SCL gedefinieerd. Deze twee lijnen creëren een synchrone seriële bus. Het aantal aan te sluiten apparaten op de bus is slechts gelimiteerd door de maximaal toegelaten capaciteit op de bus van 400 pF. Omdat de meeste ICs met een I²C inteface gebruik maken van low-power CMOS technologie met een hoge ingangsweerstand kunnen veel ICs worden verbonden met de I²C bus voor de maximale capaciteit is bereikt. Het kloksignaal op de bus wordt gegenereerd door één van de masters die met de I²C bus is verbonden. Als er geen communicatie plaatsvindt worden de SDA en SCL lijnen met een pull-up weerstand naar de voedingsspanning getrokken.

Voedingsspanningsniveaus zijn flexibel. Het is mogelijk om een 5 VDC voeding voor de bus en componenten te gebruiken, maar zelfs spanningen van minder dan 2 VDC kunnen worden gebruikt. Hierdoor kan de I²C bus worden geïmplementeerd in vele soorten circuits zonder de noodzaak van een eigen voeding. Level shifters kunnen worden gebruikt wanneer een I²C bus twee subsecties bevat met verschillende voedingsspanningen, bijvoorbeeld 3,3 Volt en 5 Volt. I²C inputs van fast mode en high-speed mode ICs gebruiken Schmitt-trigger logica om de effecten van storingen te verminderen.

Start en stop condities op de I²C interface

Alleen masters kunnen dataoverdracht initiëren op de I²C bus. Wanneer een master op de I²C bus wenst te communiceren met een slave moet het zich eerst de controle over de bus toe-eigenen. Dit is alleen mogelijk wanneer de bus idle is, dat wil zeggen dat zowel de SDA als de SCL lijn hoog zijn. De master creëert een START conditie om andere apparaten op de I²C bus te melden dat het de bus overneemt. Om een START conditie te genereren blijft de kloklijn SCL hoog, terwijl de master de SDA lijn omlaag brengt. Dit is een unieke situatie. Tijdens een normale dataoverdracht zal de SDA datalijn alleen van toestand wijzigen wanneer de SCL kloklijn laag is. Elk apparaat op de I²C bus weet dat een nieuwe communicatie sessie start wanneer de datalijn naar laag gaat terwijl de kloklijn nog hoog is. Hiermee is hersynchronisatie mogelijk wanneer er fouten zijn opgetreden in de vorige dataoverdracht en apparaten de synchronisatie zijn kwijtgeraakt.

Het einde van een communicatiesessie wordt aangegeven met een STOP conditie. De STOP conditie wordt gegenereerd door de SDA datalijn hoog te maken terwijl de kloklijn SCL ook hoog is. Net als bij de START conditie kan deze verandering van de SDA lijn niet plaatsvinden tijdens een normale dataoverdracht en aangesloten ICs kunnen hun interne communicatielogica zo resetten wanneer de vorige transfer in een fout is geëindigd. Nadat de STOP conditie is gegenereerd wordt de I²C bus geacht vrij te zijn voor een nieuwe communicatiesessie wanneer een gedefinieerde tijd is verstreken. Deze tijd is afhankelijk van de bussnelheid.

Meerdere herhaalde START condities kunnen voorkomen wanneer een START conditie wordt gegenereerd zonder een STOP conditie die de voorgaande transfer sessie beëindigd. Na een herhaalde START conditie blijft de bus bezet en daarom kan deze situatie in het algemeen worden gezien als een normale START conditie.

Dataoverdracht met I²C

Tussen de START en STOP condities vindt de dataoverdracht plaats. De eenheid van de datatransfer op de I²C bus is de byte. Data wordt van de master naar de slave overgedragen, of terug naar de master in bytes. Het eerste byte in elke dataoverdracht is het adres van de slave. Slechts zeven van de acht bits in het adresbyte worden gebruikt om het slave adres de definiëren. Het laagste orde bit geeft aan of het een lees of schrijfopdracht is. Een laag bit geeft een schrijfopdracht aan, terwijl een hoog bit een leesverzoek inhoudt. Bij de dataoverdracht wordt het meest significante bit het eerst verstuurd.

Tijdens de dataoverdracht wijzigt de master de toestand van de kloklijn SCL periodiek van hoog naar laag en terug. Data op de SDA lijn mag alleen worden gewijzigd wanneer de SCL lijn in de laag toestand is. Nadat de SDA lijn is gewijzigd naar de gewenste bit waarde wordt de SCL lijn weer hoog gemaakt om aan de andere ICs op de I²C bus te melden dat er een geldig data bit aanwezig is op de lijn. ICs op de I²C bus hebben vaak een zeer gelimiteerd geheugen, logica en snelheid. Daarom moet elke verzonden byte worden bevestigd door de ontvanger. Wanneer een master een byte heeft verzonden zendt het een negende klokpuls waar tijdens de bevestiging plaats zou moeten vinden. Zoals al eerder gezegd wordt de hoog status van de SDA lijn verzorgd door een pull-up weerstand. De slave moet de SDA lijn omlaag trekken tijdens de negende klokpuls. Wanneer dit niet gebeurt en in plaats daarvan blijft de SDA lijn hoog, weet de master dat een fout is opgetreden tijdens de dataoverdracht.

Wanneer een slave bezig is met een opdracht, of eenvoudigweg zeer langzaam in zijn functioneren en het kan niet een volgende byte ontvangen voor de vorige is verwerkt, dan kan de periode na het negende bevestigingsbit worden gebruikt om de master te laten wachten. Opnieuw is hier de logica om de master af te remmen heel eenvoudig. Wanneer de master een nieuw byte wenst te verzenden moet de master de SCL lijn naar de laag toestand brengen. De master wijzigt daarna de SCL lijn naar zijn hoog toestand door zijn uitgang in hoge impedantie te schakelen. Normaal zal de pull-up weestand de toestand van de SCL lijn naar hoog brengen, maar wanneer de slave de communicatie wil vertragen trekt het eenvoudigweg de SCL lijn naar de lage toestand voor de periode die het nodig heeft om zijn voorgaande activiteiten te beëindigen. De master kan alleen de dataoverdracht continueren wanneer het detecteert dat de SCL lijn weer in de hoge toestand is. Hiermee is een zeer eenvoudige en effectieve methode gecreëerd om langzame slaves met gelimiteerde verwerkings- en geheugencapaciteit te laten communiceren met snellere masters. Wanneer alle bytes zijn ontvangen verwerkt wordt de STOP conditie door de master gegenereerd om de bus vrij te geven voor andere communicatie.

Speciale situaties: synchronisatie en arbitrage

Eén van de krachtige eigenschappen van de I²C bus is de mogelijkheid om meer dan één master op de bus aan te sluiten. Dit kan echter problemen opleveren. Ten eerste genereert elke master zijn eigen kloksignaal. Kloksignaal perioden kunnen onderling verschillen wat synchronisatieproblemen kan opleveren. Bovendien moet een systeem worden geïmplementeerd om te voorkomen dat meer dan één master actief is op de bus op elk gegeven moment. Beide problemen worden opgelost door de synchronisatie en arbitrage logica in de I²C bus masters.

Elke I²C master heeft twee interne tellers. Eén teller wordt gebruikt om de lengte van de hoog periode van de SCL kloklijn van de I²C bus te tellen, de andere wordt gebruikt voor het tellen van de lengte van de lage toestand op de SCL lijn. Wanneer er slechts één master op de bus aanwezig is bepalen deze twee tellers samen de klokfrequentie. Wanneer twee of meer I²C masters parallel zijn verbonden kan het voorkomen dat deze tellers niet op dezelfde snelheid lopen. Dit is waar synchronisatie zijn werk doet. Zoals al eerder beschreven wordt de SCL kloklijn van de I²C bus naar de hoge toestand getrokken door een pull-up weerstand die met de voedingsspanning is verbonden. Beschouw nu de situatie waarbij de SCL lijn in de hoge toestand is, en alle interne tellers van de aangesloten masters tellen tot het moment is bereikt waarop de lijn naar de lage toestand moet worden overgeschakeld. Zodra één van de masters op de bus de SCL lijn omschakelt naar de lage toestand detecteren de andere masters deze situatie en resetten hun interne teller, onafhankelijk hoeveel die eigen teller nog had moeten tellen. Ze schakelen daardoor allemaal over naar de lage toestand en de lage periode tellers beginnen met tellen.

Na een bepaalde tijd zal de eerste van deze lage toestand tellers zijn eind bereiken en die I²C master zal beslissen om de SCL lijn weer naar de hoge toestand te schakelen. Vanwege het fysieke ontwerp van de bus waarbij een pull-up weerstand wordt gebruikt om de hoge toestand te initieren zal de SCL kloklijn niet naar de hoge toestand schakelen zolang er tenminste één I²C master nog de lengte van de lage toestand aan het tellen is. Wanneer de laatste I²C master beslist om de SCL lijn om te schakelen naar de hoge toestand zal de kloklijn van toestand veranderen. Alle masters met snellere counters hebben gewacht op dit moment waarbij de toestand van de lijn omschakelt, en zij starten allemaal met het tellen van de lengte van de hoge toestand. Met dit systeem van synchronisatie wordt de lengte van de hoge toestand van de SCL kloklijn bepaald door de snelste I²C master die op de bus aangesloten is en de lengte van de lage toestand door de langzaamste deelnemer.

Arbitrage is een ander interessant geval. Beschouw de situatie waarbij de I²C bus niet actief is en twee of meer masters op hetzelfde moment beslissen om een communicatie sessie te starten. Een procedure is noodzakelijk om te beslissen welke master het recht op de bus krijgt, en welke master moet wachten op de volgende niet actieve periode. Deze procedure wordt arbitrage genoemd.

We weten al, dat een master een communicatie sessie start met de START conditie. De SDA lijn wordt naar beneden getrokken terwijl de SCL kloklijn hoog blijft. Wanneer twee masters dit op hetzelfde moment doen kunnen ze niet detecteren of de START conditie is veroorzaakt door hun eigen actie, of door een andere master. Daarom zullen zijn doorgaan met hun protocol en de eerste databyte verzenden naar de gewenste slave. Elke keer wanneer een bit wordt gezet op de SDA lijn, controleert de master vervolgens welke waarde aanwezig is op de SDA lijn. Een master kan alleen de SDA data lijn naar een lage toestand trekken, maar niet naar een hoge. Wanneer de master een hoog bit wilde verzenden, maar het detecteert een lage waarde op de SDA lijn nadat de SCL kloklijn naar de hoge toestand is gegaan, dan weet het dat een andere master ook op datzelfde moment aan het zenden is. De master die als eerste deze situatie detecteert breekt onmiddellijk de communicatie af en zal het later opnieuw proberen. De andere master vervolgt de communicatie en krijgt prioriteit toegewezen over de I²C bus. Het kan een behoorlijk aantal bits kosten voordat een master detecteert dat een andere master ook informatie verzendt. Speciaal wanneer beide masters dezelfde slave adresseren—wat resulteert in hetzelfde bitpatroon in het adresbyte—kan het een behoorlijk aantal bits kosten voordat één van de masters de communicatie afbreekt. Dit heeft echter geen negatieve invloed op de communicatie van de andere masters omdat er geen bits zullen zijn verminkt.

Een speciale situatie treedt op met ICs die zowel als master als slave functioneren op dezelfde I²C bus. Wanneer arbitrage plaatsvindt kan het zijn dat de verliezende master feitelijk de slave is waarmee de winnende master contact probeert te maken. In dergelijke gevallen moet de verliezende master direct omschakelen naar slave mode en de reeds verstuurde bits interpreteren om te zien of zijn slave adres door de andere master is geselecteerd.

|

The sum of the intelligence on the planet is a constant;

the population is growing.

MR. COLE'S AXIOM

|